Code 000 2 2s Complement of A op. Jan 20 2018 - Verilog code for Multiplexers.

Vhdl For Fpga Design 4 Bit Alu Wikibooks Open Books For An Open World

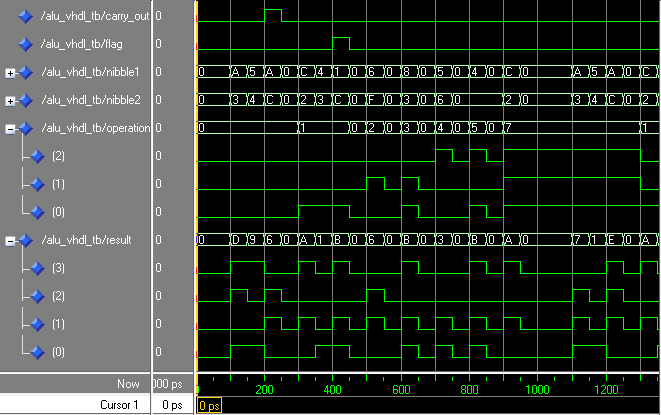

Simulation of 4-bit 32-bit ALU and Imlementation using FPGA in chapter 5 6.

. Design methodology has been changing from schematic design to HDL based design. Department of Electronics and Communication Engineering Athihrii Stephen Sanjay 2016 Page 19 Design and implementation of 32-bit ALU using Verilog 2016 Fig34 Arithmetic Logic Unit 32. 4 bit ALU Design in verilog using Xilinx.

The design was implemented using VHDL Xilinx Synthesis tool ISE and targeted for Spartan device. Make sure you have installed Xilinx ISE 144 or later. It can be used in integer arithmetic computations and as Complex operation.

Design a 4-bit ALU that implements the following set of operations with only the following components assume 2s complement number representation no need to implement overflow circuit 1-bit Full-Adders FA 2-input ANDORXOR gates Inverters 21 MUX 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 0 1 0 1 0 1 0 Add Subtract Increment. I am supposed to create 4 bit full adder verilog code in vivadoBut when I try to test in the simulationIt give me z and x outputWhich part of code I have to change to get an output in simulation. In this paper we present the design of an.

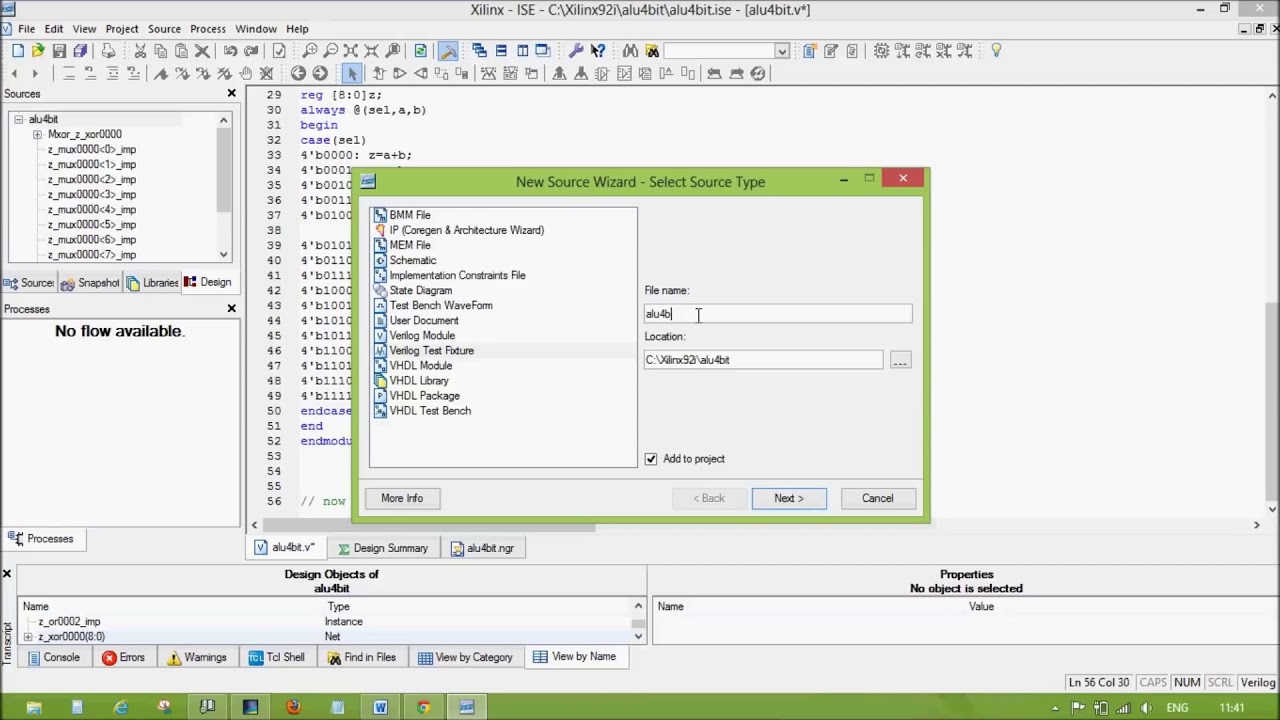

Open 3264-bit Project Navigator. Follow the below-mentioned procedure to simulate your first Verilog program. Table of 32-bit Arithmetic Logic Unit 31.

Im struggling with the code to make a 4-bit ALU in Verilog. N-bit Adder Design in Verilog. In this tutorial we will walk you through the steps on how you can simulate a Verilog program in Xilinx Project Navigator.

4 - bit ALU using Verilog. When M0 and the result from the 4-bit ALU is Logic based the result is displayed on an array of LEDs. Ive created and tested the code for a 1-bit Half Adder a 1-bit Full Adder a 4-bit Ripple Adder and 2s complement coding.

Here verilog HDL was coded using Quartus II 90 version software and 4 bit ALU hardware design was done using Proteus software. Each module of ALU is divided into smaller modules. Ive created and tested the code for a 1-bit Half Adder a 1-bit Full Adder a 4-bit Ripple Adder and 2s complement coding.

Ac89774 on Mar 29 2017. This paper presents design concept of 4-bit arithmetic and logic unit ALU. INTRODUCTION A 64-bit ALU implemented using VHDL and verified on Xilinx ISE simulator.

However I need perform this additional coding. Code 011 5 4 input NOR operation using dynamic NOR gate op. Code 100 6 1s Complement of B op.

4-bit ALU Module Name. For this tutorial we have Xilinx ISE 144. 3 Sri Venkateswara Engineering College.

Mohd Kashif Create Date. There are 6 different functions implemented in this ALU. 131230 07012013 Design Name.

Include addition subtraction and shifting We proposed arithmetic and logic unit using VHDL structural and dataflow level design. On the other hand when M1 the. 1 4 bit Addition op.

All the modules in arithmetic and. Today fpga4student presents the Verilog code for the ALU. Verilog of 4 bit ALU structural Code is shown in Appendix A.

The approach used here is to split the ALU into three modules one Arithmetic one Logic and one Shift module. Verilog code for Arithmetic Logic Unit ALU Last time an Arithmetic Logic Unit ALU is designed and implemented in VHDL. Add A B 4b0000 add A B C 4b0010 add A - B 4b0010 Logical Shift Right.

ALU Behavioral Project Name. AIM The main aim of this project is to design and simulation of different 8-bit multipliers using VERILOG code Considering their advantages and disadvantages these are compared on the basis of area speed and delay. The testbench Verilog code for the ALU is.

The arithmetic logic and shift units. This is a repository for our EEE 304 course project. Each module of ALU is divided into smaller modules.

This video describes the complete simulation flow step by step for VHDL Code using Xilinx ISE Design Suite 147 It helps beginners to understand the working. In this Video you will learn how to design or implement the 4 bit ALU in verilog using Xilinx Simulator in very simple waySee Code here httpwww2dixco. 32 bit adder subtractor ALU using generate.

- GitHub - aia39Arithmetic-Logic-Unit-ALU-Design-and-Simulation-In-Verilog-and-Proteus. We proposed arithmetic and logic unit using VHDL structural and dataflow level design. Code 001 3 4 bit Add-traction op.

Design methodology has been changing from schematic design to HDL based design. 4-Bit ALU in Verilog. Code 010 4 4 input NAND operation using static NAND gate op.

Execute was to design a 1-bit ALU and then combine four of them to create a 4-bit ALU. Since the output of the 4-bit ALU F30 is dependant on the signal M we have two ways of displaying our results. Up to 24 cash back Im struggling with the code to make a 4-bit ALU in Verilog.

This research paper is based on the simulation of 16 bit ALU using VHDL. Mihir Gajjar and Mihir Gajjar 4 - bit ALU using Verilog. For shifter unit the selection line S1 is used to select either left or right shift micro-operation.

An ALU performs following operations Addition subtraction multiplication Not logical shift right logical shift left rotate right rotate. The project is a 4-bit ALU in VHDL with a total of 16 operations which includes various arithmetic logical and data calculations performed by coding the ALU in VHDL code. Full VHDL code for the ALU was presented.

This paper presents design concept of 4-bit arithmetic and logic unit ALU. Keywords- ALUArithmetic Logic Unit LULogic Unit RTLRegister Transistor View Shift Unit VHDL. The name of the course is Digital Electronics Laboratory.

4 Bit Alu Design In Verilog Using Xilinx Simulator Youtube

Verilog Code For Arithmetic Logic Unit Alu Fpga4student Com

Xilinx Ise 4 Bit Alu Add Subtract Verilog Youtube

Lesson 60 Example 36 4 Bit Arithmetic Logic Unit Alu Youtube

0 comments

Post a Comment